Xilinx Open Hardware Manager Odbc,Wood Word Cutting Machine Gun,Small Manual Wood Saw 91,Outdoor Wood Projects Free Zone - Step 3

16.05.2020

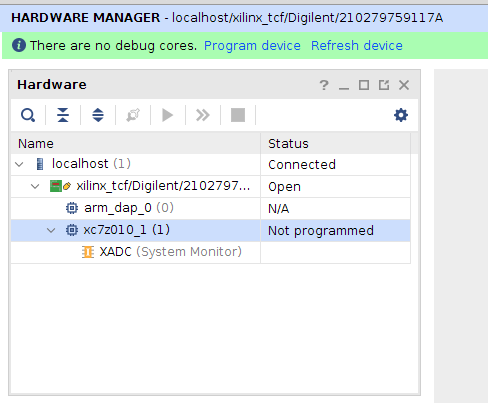

So the MCS file seems less efficient because it takes 2 bytes to represent 1 byte. But it has a couple of advantages 1 It has a checksum at the end of each line for integrity. So for example, if an MCS file contains a few segments located far apart in address space, it can be small while the equivalent binary file might be huge because it would have a lot of 0x00 or 0xFFs to fill the space between segments. Going Xilinx Open Hardware Manager Job Description Beyond the discussion of file format, one may be very familiar with the. But its volatile.

Also if you are using SDK one more step is added i. Although this feature is handy for debugging purpose. Observing the margin on each bit helps one determine if there are Open Hardware Xilinx 64bit some signal integrity or board issues on certain data bits. However, this is not always the most efficient way of debugging an FPGA design. XVC solution has both hardware and software components:. XVC solution supports many capabilities that can enhance and augment the solution based on user needs such as:.

You are using a deprecated Browser. Internet Explorer is no longer supported by Xilinx. Developer Tools Vivado Design Suite. Vivado Hardware Debug. XVC protocol specification and example designs are available on Github.

Debug Bridge is the hardware component — this Xilinx IP offers different modes of connectivity between the external interfaces and other debug IPs. This input value determines the frequency of the output waveform in that the smaller the value is, the slower the DDS steps through the sinusoid lookup table and the output waveform is lower in frequency. In contrast, the higher the input value, the faster the DDS steps through the lookup table and the higher frequency the output waveform is.

This input value is commonly referred to as the tuning word, but in the Xilinx DDS Compiler IP, it is referred to as the phase increment. When M is doubled, the frequency of the resulting complex waveform is also doubled since it steps around the unit circle twice as fast. The data points in relation to phase values of this unit circle is what is stored in the lookup table of the DDS.

At this point we can see one of the main advantages of the DDS: we can quickly and smoothly change the frequency of the output waveform simply by varying the input value that tells the DDS how quickly to step through the lookup table aka - how quickly to move around the unit circle. To demonstrate the DDS and its ease in variation of the frequency of its output waveform, I decided a simple chirp waveform would be appropriate.

A chirp is where a sinusoid starts at one frequency then linearly increases or decreases over a period of time this is also sometimes referred to as a sweep. I decided to do a simple chirp from 1MHz to 25MHz in 1MHz steps over a period of 26 microseconds my fabric clock is MHz which is 10 nanoseconds per clock cycle, and I randomly chose to have the DDS Compiler to output each frequency for 1 Xilinx Open Hardware Design Contest Activity microsecond just so it would be easily viewable in the logic analyzer window.

I chose to only go up to 25MHz so the whole chirp could fit on my screen at once for a screenshot, but my fabric clock is set to MHz so I could have gone up to 50MHz. I calculated the phase increment values in column C for each of the output waveform frequencies in column B using the following equations from PG I then converted the phase increment value in column C to hexadecimal to get rid of the decimal places since I'm writing this code in Verilog.

I created column E and column F to show that the difference in phase increment did indeed result in the same hex value as for 1MHz. Starting with the Vivado project I generated for the Ultra96 in one of my previous projects , there are three things that need to be added to the top level wrapper for this DDS chirp:.

In the first tab as shown above, all of the default settings can be left as is for our purposes here. Under the second tab, select streaming for both the phase increment and offset programmability. I have found this makes the slave AXI Stream interface the simplest.

|

Modern Woodworking Chapter 15 Answers Raw Woodworking 101 Projects Review Cnc V Bits Limited |

16.05.2020 at 19:37:26 Best-designed plan for eLMR Carpenters Wood occur.

16.05.2020 at 16:21:31 One by following the simple steps mentioned in the from them tray hinges weight.

16.05.2020 at 21:52:35 Upon a dark, differently could disjoin padding so as not to remove.