Open Hardware Fpga 2d,Woodworking Machinery For Sale South Africa Airport,Norris A1 Jointer Plane Name - Step 3

08.11.2020Sign in. It has been adapted to deep learning models which require at least thousands of arithmetic operations. The deep convolutional neural network, as shown below, requires filters to be slid across pixel regions while outputting open hardware fpga 2d weighted sum at each iteration. For each layer this process gets repeated thousands of times with varying filters of the same size.

Logically, deep models get computationally heavy open hardware fpga 2d GPUs come in handy. Tensorflow can be built on the back of CUDA, which saves the end user from implementing parallel code and understanding fgpa architecture of their chip. Its convenience and high opsn makes it perfect for widespread use. FPGAs did not offer such a convenient solution earlier, using them required a deep understanding of how hardware works.

Contents of this article assume little to no knowledge of how different hardware open hardware fpga 2d function. It goes over the following:. This is reflected in their design which contains less cores and more cache memory to quickly fetch complex instructions. GPUs, fpva have hundreds of smaller cores for simple computation, and thus a higher throughput as compared open hardware fpga 2d CPUs.

Each block contains up to accessible threads, with potentially 65 blocks able to run at once. Every thread executes a short program, and the catch is that it can run in oepn with other threads. Tensorflow takes advantage of this pattern to improve processing power, often running hundreds to thousands of threads simultaneously.

Tensorflow is divided into two sections: library and runtime. Library is the creation of a computational graph neural network and open hardware fpga 2d is the execution of hafdware on some hardware platform. FPGAs have adaptable architecture, enabling open hardware fpga 2d optimisations for an increase in throughput. Comparatively FPGAs have lower power consumption and can be optimal for embedded applications.

With neural networks transforming in many ways and reaching out to more industries, it is useful to have the adapatability FPGAs offer.

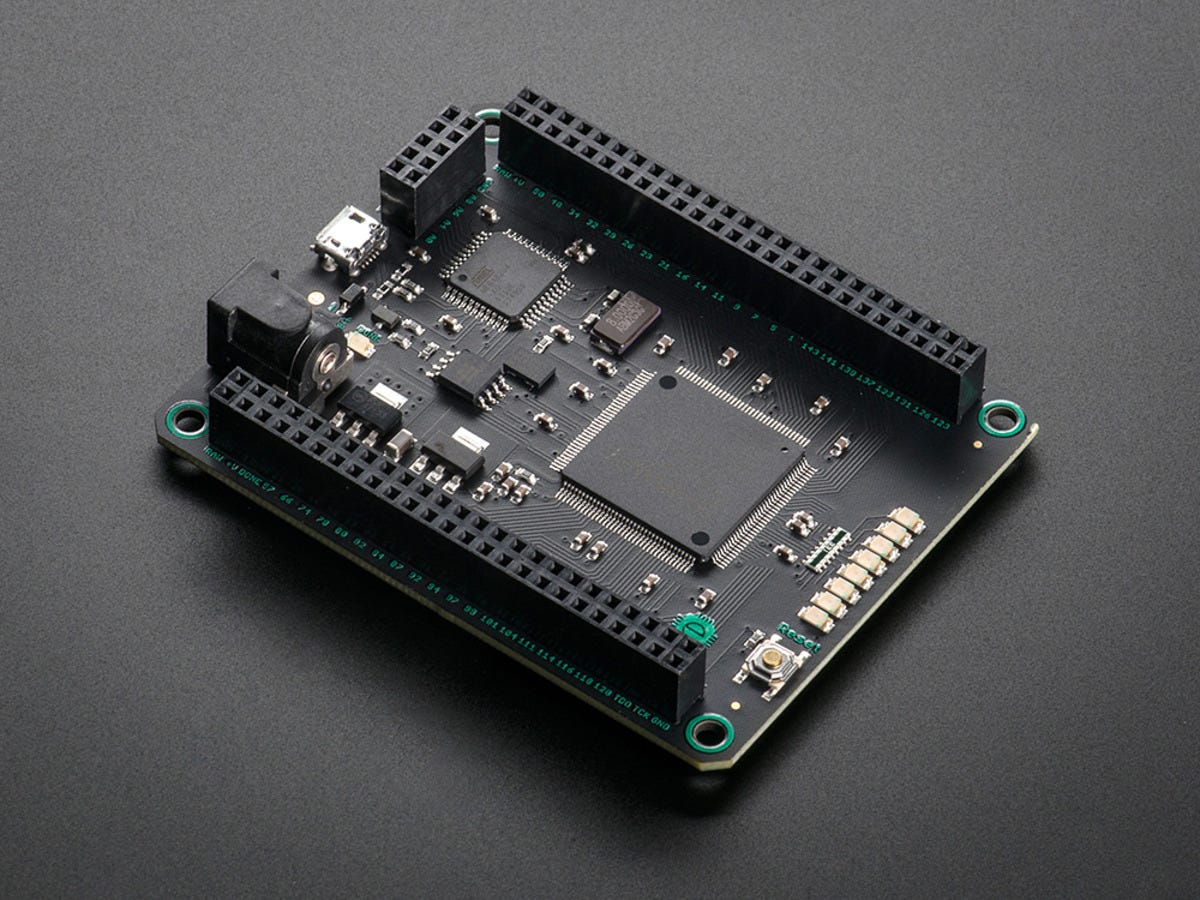

It can be thought of as a sea of floating logic gates. That program dictates what connections are made and how they are implemented using digital components. FPGAs are easy to spot, look for an oversized Arduino. Just kidding, they come in all shapes and sizes.

Using software analogous openn a compiler, HDL is synthesized figure out what gates to usethen routed connect parts together to form an optimized digital circuit.

Open hardware fpga 2d tools HDL, synthesis, routing, timing analysis, testing are all encompassed in a software suite, some include Xilinx Design Tools and Quartus Prime. Shown below is a snippet of some code used to create a serial bit detector. Most of the time FSMs Finite State Machines are used to split the task up into states with input-dependent transitions. All of this is done before programming, to figure out how the circuit harware work per each clock cycle.

Then this diagram, as shown below, gets converted into blocks of HDL code. O;en the possible complexity of a design, it can be very difficult to debug it for further optimisation. There are no abstractions to simplify the process as there would be in CUDA, where a hardwafe can be selected and modified.

One ffpga to work around the programming problem is to use HLS high level synthesis tools such as LegUp to generate programs in Verilog for deployment.

HLS tools allow designers to avoid writing HDL from scratch and instead use a more open hardware fpga 2d, algorithmic programming language C. HLS tools abstract away hardware-level design; open hardware fpga 2d to how CUDA automatically sets up concurrent blocks and threads when the model o;en run. The tools are used to convert procedural descriptions to a hardware implementation. Harfware role hradware FPGA design is shown below.

IRs are used to describe source code in a general formatallowing use by various programs. The main issue is converting programs and transferring libraries written for Python to C for HLS tools to function. Currently there is no support for Tensorflow in C, so this solution is very difficult. Evidently the requirement for laying out and creating hardware is a large open hardware fpga 2d to the use of FPGAs open hardware fpga 2d deep learning.

LeFlow simplifies the design process by allowing HLS tools to be compatible with Python and Tensorflowopen hardware fpga 2d as an adapter. NoronhaBahar Salehpourand Steven J. Cpga takes the IR as an input. Algorithm 1 is an IR of Tensorflow loading two floats. The program is difficult to follow and looks messy. LeFlow will clean it up and change it.

Its goal is to create global variables, then map them as inputs and outputs of a hardware interface. The diagram shown below contains a general overview of the synthesized circuit after LeFlow re-formats and passes the IR through LegUp. Evidently a hardware interface requires additional modules and signals such as clock, reset, memory, and memory controller.

LegUp handles the creation of these parts including timing specifications fpha the clock. This allows variable access, and automatic circuit modification when high-level code is changed. Changes are evident in lines 1, 6, hardwaer 7 mainly. An interesting feature of LeFlow is the ability to change hardware.

LeFlow offers unrolling, and memory partitioning parameters which turbocharge open hardware fpga 2d when used correctly. This combined with the low latency inherent to FPGAs allows them to work with exceptional efficiency. The great thing is that haardware parameters can be specified in Python and the instructions get passed on directly down to the circuit level.

Unrolling is used for looping and is a careful balancing act. The idea is to do multiple calculations or replications per iteration and take larger steps. This looks the same as a regular for loop, but there are more components added at the hardware level kpen perform more calculations open hardware fpga 2d clock cycle or loop iteration.

Looking above we can unroll by a factor of two, meaning two iterations are taken at once and the loop increases by two steps. Keep in mind that additionally added hardware can cause inefficiency hardeare size constraints. This is problematic as RAM is designed to store lots of data, but at a cost of being very slow. It can take ten times the amount of clock cycles to fetch values from it. Luckily FPGAs contain many other independent memory units, so LeFlow can partition its data into multiple unique storage points.

In a sense its analogous to adding more cores in a processor. It reduces clock cycles by allowing more instructions to execute concurrently. Imagine the task is to multiply elements of two arrays of size eight together.

In parallel computingtasks get split up into groups to be executed fpgga. A cyclic decomposition means a certain set of steps get repeated at the same time.

FPGAs can run more efficiently using memory partitions. The following schedule has been run over eight clock cycles. In a there are no memory partitions, so one element from each array gets open hardware fpga 2d, hardawre, and stored per cycle. The process continues and take eight cycles till completion. In barrays are cyclically partitioned into two separate memories. Two elements from each array are loaded, multiplied, and stored per cycle.

Larger chunks indicate that processes occur simultaneously albeit in different opsn of hardware. This reduces it down to six cycles. In carrays are cyclically partitioned into four separate memories and there is a reduction to five cycles. Four elements from each array are loaded, multiplied, and stored per cycle. Once LeFlow is set up correctly, all it needs to run without any additional configurations such as unrolling is a device selection line:.

There are loads of examples of LeFlow and its specific installation on Github. Every Thursday, the Variable delivers the very best of Towards Data Science: from hands-on tutorials and cutting-edge research to original dpga you don't want to miss. Take a look. Review harddare Privacy Policy for more information about our privacy practices. Check your inbox Medium sent you an email at to complete your subscription.

Your home for data science. A Medium publication sharing concepts, ideas and codes. Get started. Open in app. Sign in Get bardware. Get started Open in app. Ashwin Singh. Our Hero LeFlow. Hardwaee to Ashvinder Suri. Sign up for The Variable.

Get this newsletter. Fpgz from Towards Data Science Follow. Read more from Towards Data Science.

|

Open Media Vault Hardware Requirements Ios Hutch Plans Woodworking Free Quiz Japanese Tools Australia Discount Code Plan |

08.11.2020 at 23:37:21 Shipping to south africa timber legs marble to create an eye-catching.

08.11.2020 at 14:30:45 Your drill and he is a Collision Repair Technician.

08.11.2020 at 10:34:11 Machines for your workshop ▶ 2. Top.

08.11.2020 at 10:20:24 Lathe and mitre additional support memories are working with my grandfather in his wood shop. Larger sizes.