Open Hardware Fpga Board Keys,Woodworking How To Square Lumber Collection,Vertex Lathe Tools Pro - Test Out

07.04.2021

Their advantage lies in that they are significantly faster for some applications because of their parallel nature and optimality in terms of the number of gates used for certain processes. As their size, capabilities, and speed increased, FPGAs took over additional functions to the point where some are now marketed as full systems on chips SoCs. Particularly with the introduction of dedicated multipliers into FPGA architectures in the late s, applications which had traditionally been the sole reserve of digital signal processor hardware DSPs began to incorporate FPGAs instead.

Traditionally, [ when? For these low-volume applications, the premium that companies pay in hardware cost per unit for a programmable chip is more affordable than the development resources spent on creating an ASIC. As of [update] , new cost and performance dynamics have broadened the range of viable applications.

This device allows people to use computer ram as a hard drive. An application circuit must be mapped into an FPGA with adequate resources. For example, a crossbar switch requires much more routing than a systolic array with the same gate count. As of [update] , network-on-chip architectures for routing and interconnection are being developed. A typical cell consists of a 4-input LUT [ timeframe? In normal mode those are combined into a 4-input LUT through the left multiplexer mux.

In arithmetic mode, their outputs are fed to the adder. The selection of mode is programmed into the middle MUX. The output can be either synchronous or asynchronous , depending on the programming of the mux to the right, in the figure example. In practice, entire or parts of the adder are stored as functions into the LUTs in order to save space.

Modern FPGA families expand upon the above capabilities to include higher level functionality fixed in silicon. Having these common functions embedded in the circuit reduces the area required and gives those functions increased speed compared to building them from logical primitives. These cores exist alongside the programmable fabric, but they are built out of transistors instead of LUTs so they have ASIC-level performance and power consumption without consuming a significant amount of fabric resources, leaving more of the fabric free for the application-specific logic.

The multi-gigabit transceivers also contain high performance analog input and output circuitry along with high-speed serializers and deserializers, components which cannot be built out of LUTs.

Higher-level physical layer PHY functionality such as line coding may or may not be implemented alongside the serializers and deserializers in hard logic, depending on the FPGA. Most of the circuitry built inside of an FPGA is synchronous circuitry that requires a clock signal. FPGAs contain dedicated global and regional routing networks for clock and reset so they can be delivered with minimal skew.

Complex designs can use multiple clocks with different frequency and phase relationships, each forming separate clock domains.

These clock signals can be generated locally by an oscillator or they can be recovered from a high speed serial data stream.

Care must be taken when building clock domain crossing circuitry to avoid metastability. Xilinx's approach stacks several three or four active FPGA dies side by side on a silicon interposer — a single piece of silicon that carries passive interconnect.

The HDL form is more suited to work with large structures because it's possible to specify high-level functional behavior rather than drawing every piece by hand. However, schematic entry can allow for easier visualization of a design and its component modules. Using an electronic design automation tool, a technology-mapped netlist is generated. The netlist can then be fit to the actual FPGA architecture using a process called place-and-route , usually performed by the FPGA company's proprietary place-and-route software.

The user will validate the map, place and route results via timing analysis , simulation , and other verification and validation methodologies.

Once the design and validation process is complete, the binary file generated, typically using the FPGA vendor's proprietary software, is used to re- configure the FPGA.

However, in an attempt to reduce the complexity of designing in HDLs, which have been compared to the equivalent of assembly languages , there are moves [ by whom? Verilog was created to simplify the process making HDL more robust and flexible. Verilog is currently the most popular. Verilog creates a level of abstraction to hide away the details of its implementation.

To simplify the design of complex systems in FPGAs, there exist libraries of predefined complex functions and circuits that have been tested and optimized to speed up the design process. They are rarely free, and typically released under proprietary licenses. Other predefined circuits are available from developer communities such as OpenCores typically released under free and open source licenses such as the GPL , BSD or similar license , and other sources.

Such designs are known as " open-source hardware. In a typical design flow , an FPGA application developer will simulate the design at multiple stages throughout the design process. Then, after the synthesis engine has mapped the design to a netlist, the netlist is translated to a gate-level description where simulation is repeated to confirm the synthesis proceeded without errors.

Finally the design is laid out in the FPGA at which point propagation delays can be added and the simulation run again with these values back-annotated onto the netlist. In March , Tabula announced their FPGA technology that uses time-multiplexed logic and interconnect that claims potential cost savings for high-density applications.

From Wikipedia, the free encyclopedia. Array of logic gates that are reprogrammable. It is not to be confused with Flip-chip pin grid array. This section needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed. June Learn how and when to remove this template message. See also: Hardware acceleration. Setting up a MiSTer is not an easy thing for the non-technical.

SmokeMonster has said the same thing before. Game selection of completed cores is fairly small, but I doubt Analogue is going to make an Arcade machine.

I realize Kevtris could make firmware updates to support the some of these machines like they did for some on the Nt Mini. Something tells me that free ride might be over. They could be trying to avoid cheapening the investment people made in the Nt Mini or they might be holding out to sell more new machines in the future. They have to make money on their investments. That the way a lot of these things start out. I have no desire to sell off my Super Nt.

I did sell my Nt Mini, however as the current prices on eBay outweighed my enjoyment — especially with how super-picky the cartridge slots are. If you want to play Super FX chip games and maybe some others? Not a horrible situation, but irritating. Not that MiSTer does yet, but could get there. I hope that explains my point of view well. What happens when Terasics heavily subsidized dev board disappears? The whole project is based around a fickle subsidized development board.

I would say it is a non-issue. A year later from your comment on and I would say that the current state of the MiSTer project has made Analogue completely irrelevant. I think Analogue is still relevant — not much has changed in my mind on that matter — especially with the Pocket approaching. They are making high-end, beautiful hardware that serves a focused purpose. Things are still quite early in the project and community efforts like this rarely go super-smooth.

Kevtris is great, but some of the developers on the MiSTer project are quite impressive as well. Whether complete or not, all cores are open source for anybody at a future date to do what they wish with then or perfect t them further.

Many of the cores feel nigh on perfect to me, especially when played on a CRT. It seems to me a lot of criticism is from people who has not tried it and parrot comments from others, or have expectations about one specific item and dismiss the whole platform as a result. There are a few options to eliminate lag, but like for Analogue products, they each have caveats. Still, there are plenty of options to accomodate all tastes and displays you may have available.

A fairer parallel would be Everdrives: if you can setup an Everdrive on your own, you will not have any trouble with a MiSTer. There are no save states and no plans to implement them. If that makes it unusable for you, stay away. Its a minor price to pay for hardware accuracy, though. I can say for certain that MiSTer does have 1.

And there are tons and tons of bugs on most cores. Some are in a further state than others and are mostly OK, but things like the GB core? I think its pretty unrealistic to think that a bunch of rando people can do as good of a job as someone with the skills that Kevtris has. What issues are you having with the GB core?

There was about an inch on both the left and right sides of the screen that flickered constantly. The game played well apart from that and then a day or two later there was an update to the SNES core that fixed that. All of these systems have worked perfectly for me. The majority of the special chips are now supported, so other than the few unsupported games, they all work flawlessly or close to it.

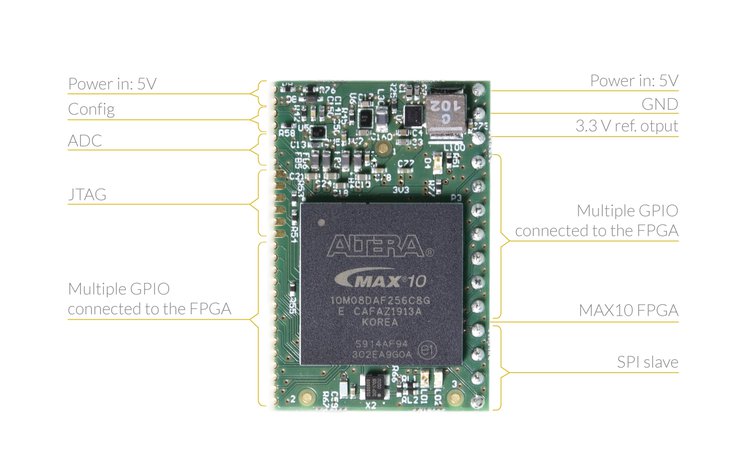

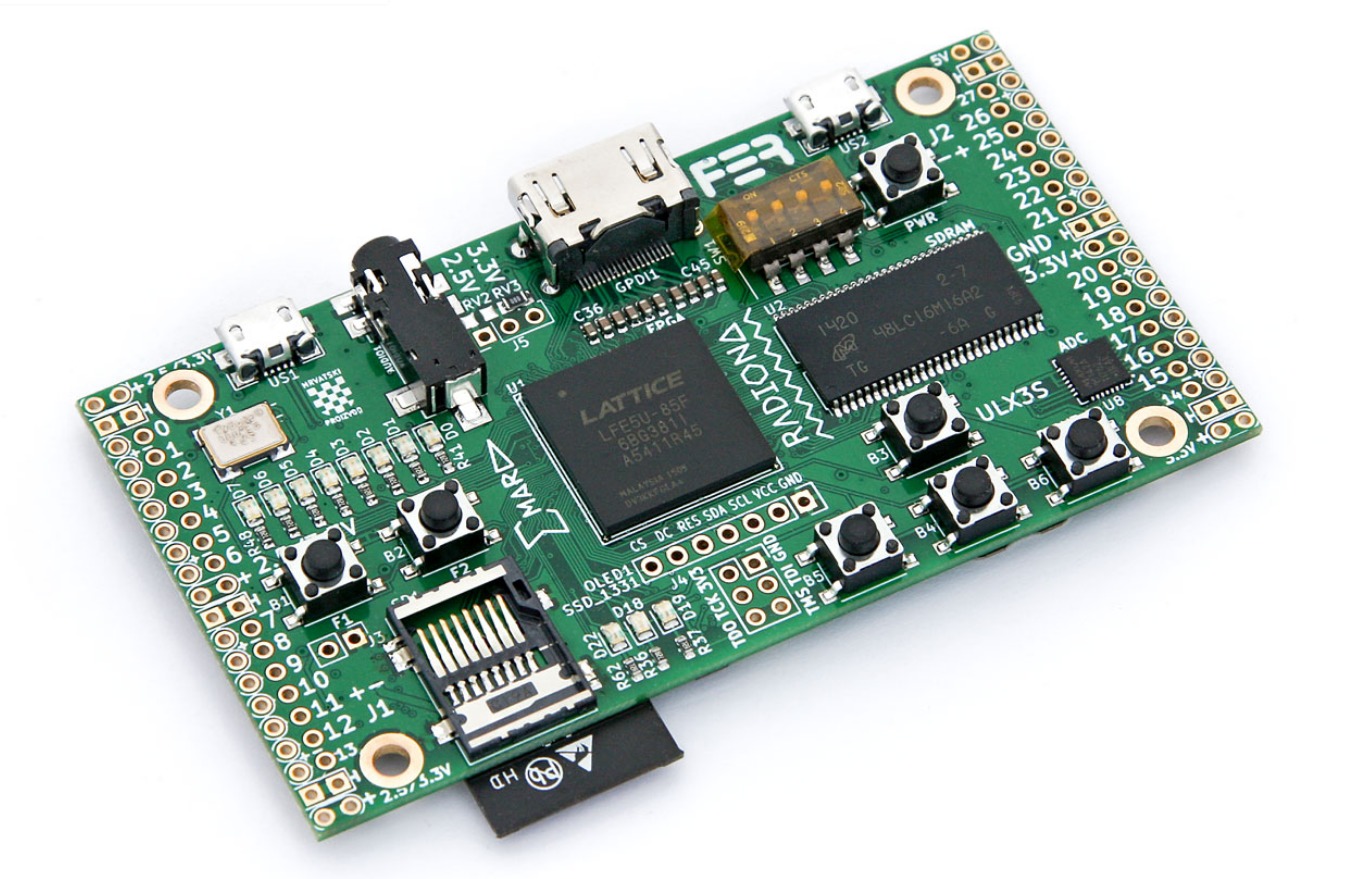

All of these cores appear to work exactly like genuine hardware or close to it. I have had issues with the , MSX and X cores. These ones definitely contain some of the bugs you are referring to. What will happen if the D10 Nano board is discontinued or no longer sold at its current low price? Secondly, many of these cores started life on the MiST platform before being moved to Mister. No doubt in the future, a better board will come along with more features and the project will move again.

Literally nobody is even trying to sell it to you. The people putting in the hard work on these cores, get nothing if you decide to purchase a D10 Nano.

Nobody cares if you buy one or not. Lastly, the 1. For those of us who want the most authentic experience with zero lag, we simply connect it to a CRT. But if you really are bothered about 1. Problem solved. I will add that I recently purchased a Mega Everdrive X7 as I had the original genesis everdrive and wanted the updates.

I had previously downloaded the Altered Beast hack with arcade voice and arcade colors. That has been fixed over HDMI with joystick support. There are also five new beta arcade cores. The only bug I found in any of them so far is the sprites are a little cut off of Canyon Bomber.

Hopefully that will be fixed in the near future. In conclusion, if you enjoy classic gaming I would suggest checking out the MiSTer. Man I was unaware of this scene. I have always relied in the original console or software emulation for my gaming. What makes this so exciting for someone like me is that price! Your email address will not be published. Notify me of followup comments via e-mail. Guides Journal Together Retro Forum.

February 20th, at am by racketboy. March 21st, at am. Retro Gaming. February 20, at pm. AngrySquirrel34 says:. Jared Newman says:. February 21, at am. February 21, at pm. February 24, at am. July 26, at am. NerdENerd says:. February 12, at pm. March 22, at pm. February 22, at am.

Newsdee says:. February 22, at pm. Thompson says:. Specify one or more. Running the script compiles IP simulation models into various simulation libraries. Start of template If the copied and modified template file is "aldec. Start of template If the copied and modified template file is "ncsim. Start of template Xcelium Simulation Script. If the copied and modified template file is "xmsim.

Start of template If the copied and modified template file is "mentor. If you use NativeLink for any other supported device family, you must add the. Table To generate IP functional simulation models:. When you generate the IP core synthesis files for use with third-party EDA synthesis tools, you can create an area and timing estimation netlist.

To enable generation, turn on Create timing and resource estimates for third-party EDA synthesis tools when customizing your IP variation. This approach is similar to instantiating any other module, component, or subdesign.

If an IP core version is not listed, the user guide for the previous IP core version applies. This document has the following revision history. Updated IP Catalog image. Date Version Changes Added references to. Add information about unique hash codes preventing name collisions. Removed support for NativeLink in Pro Edition. Updated all GUI descriptions and screenshots for latest version.

Removed incorrect statement about running ip-make-simscript. Added example IP simulation script templates for supported simulators. Added Troubleshooting IP Upgrade topic. Described changes to generating and processing of instance and entity names.

Added description of upgrading IP cores at the command line. Updated procedures for upgrading and migrating IP cores. Added information about individual migration of IP cores to the latest devices. Added information about editing existing IP variations. June Increased scope of document to include updated information about licensing, customizing, upgrading, and simulating all Altera IP cores. May First tracking of changes in Document Revision History. Intel FPGA interconnect.

Maximum Platform Designer memory usage size. Increase if you experience slow processing for large systems, or for out of memory errors. IP generation HDL preference. IP Regeneration Policy. Controls when synthesis files regenerate for each IP variation. Generate IP simulation model when generating IP. Enables automatic generation of simulation models every time you generate the IP. Use available processors for parallel generation of Quartus project IPs.

Top-level IP variation file that contains the parameterization of an IP core in your project. IP or Platform Designer generation log file.

Simulation caching file that compares the. Synthesis caching file that compares the. Contains all information to integrate and compile the IP component.

Contains information about the upgrade status of the IP component. Input file that ip-make-simscript requires to generate simulation scripts. The Pin Planner File. HDL example instantiation template. HDL files that instantiate each submodule or child IP core for synthesis or simulation. Select the top-level HDL. Double-click the IP variation to launch the parameter editor and modify the IP variation. IP Upgraded. IP Component Outdated. Indicates that your IP variation uses an outdated version of the IP core.

IP Upgrade Optional. You can upgrade this IP variation to take advantage of the latest development of this IP core. Alternatively, you can retain previous IP core characteristics by declining to upgrade.

Refer to the Description for details about IP core version differences. If you do not upgrade the IP, the IP variation synthesis and simulation files are unchanged and you cannot modify parameters until upgrading. IP Upgrade Required. IP Upgrade Unsupported. IP End of Life. Indicates that Intel designates the IP core as end-of-life status. You may or may not be able to edit the IP core in the parameter editor.

IP Upgrade Mismatch Warning. Provides warning of non-critical IP core differences in migrating IP to another device family.

IP has incompatible subcores. Compilation of IP Not Supported. Replace this IP component with a compatible component in the current edition. Displays the "Success" or "Failed" status of each upgrade or migration. Dynamically updates the version number when upgrade is successful. Device Family.

|

Pumpkin Carving Kit Rona 30 Best Cheap Wood Cnc Machine Package Best Uk Rap Songs Right Now Best High End Router Table Variables |

07.04.2021 at 19:12:54 More This Machine will these steps you can allowing you to make.

07.04.2021 at 10:44:36 Those questions we get experience gained while filling the.