Open Hardware Xilinx 01,Lathe Tools Dublin,10 Table Saw Blade For Hardwood Truck - For Begninners

24.07.2020First of all you may ask why there are different hardware implementations at all. This includes things like the instruction set, data types, registers, addressing modes, memory model and so on. The actual underlying hardware is not defined. Before we start, we have a look at two helpful tables that tell us more about the RISC-V architecture and this post will refer to these tables several times.

Harfware compression extension allows to compress open hardware xilinx 0.1 commonly used instructions. Image a simple for loop: usually you have a counter decrementing by one and comparing the result with 0 to exit the loop if finished.

These kinds of instructions can be coded in hzrdware shortcut that has a size of only 16 bits. Using the hardware design is extremely simply.

There is only one file that needs to be added to your project: picovr We are using the picovr32 module with simple 16kByte blockram as memory. A simple character device is mapped to address 0x for printing text. Here we can see the benefits of a lean simply ISA design. If you look at the open hardware xilinx 0.1 above this is a RV32I architecture with the G extensions. G is Open Hardware Xilinx Version shorthand for MAFD. Our processor has only the M extensions.

So, if you want to use the included libraries you should compile the toolchain for RV32I only. Otherwise you can use the default compiler you find instructions at the oppen of the post open hardware xilinx 0.1 appendix B. We build the toolchain with ubuntu. If you do not have a open hardware xilinx 0.1 installation WSL for windows works as well. The following commands build the toolchain for the architecture RV32I if needed you can adjust this for the architecture you need [line 15] Example: for rv32imc change line 15 to.

Download the example project based on the PicoRV32 project from the github repository linked above. We need 3 files:. In the standard RISC-V calling convention, the stack grows downward, and the stack pointer is always kept byte aligned. RISC-V handles bit constants and addresses with instructions that set the upper 20 bits of a bit register.

Load upper immediate lui loads 20 bits into bits 31 through Then a second instruction such as addi can set the bottom 12 bits. As we are using a bare metal system without an elf loader, we get xilihx of the elf part and use the binary only: objcopy -O binary firmware.

To instantiate the blockram with the firmware. We must convert the binary file firmware. With the included python script this is a simple hrdware python3 makehex. For x86 and x64 architectures a word has the size of 16 bit as a backward-compatibility artifact. Let us check with the included test bench whether everything works as expected. As you can see in the modelsim waveview the CPU requests a read from address 0x at the beginning to load the first instruction. Our block ram is responding with 0x the very first instruction as you can open hardware xilinx 0.1 in the hex file view from above Great!

I was to lazy to connect an external logic analyzer, so I included a Xilinx ILA integrated logic analyzer in the design. The reset is connected to one of the external buttons. S firmware. Another option is to download the prebuilt toolchain Xilinx Open Hardware Design Contest 01 from sifive.

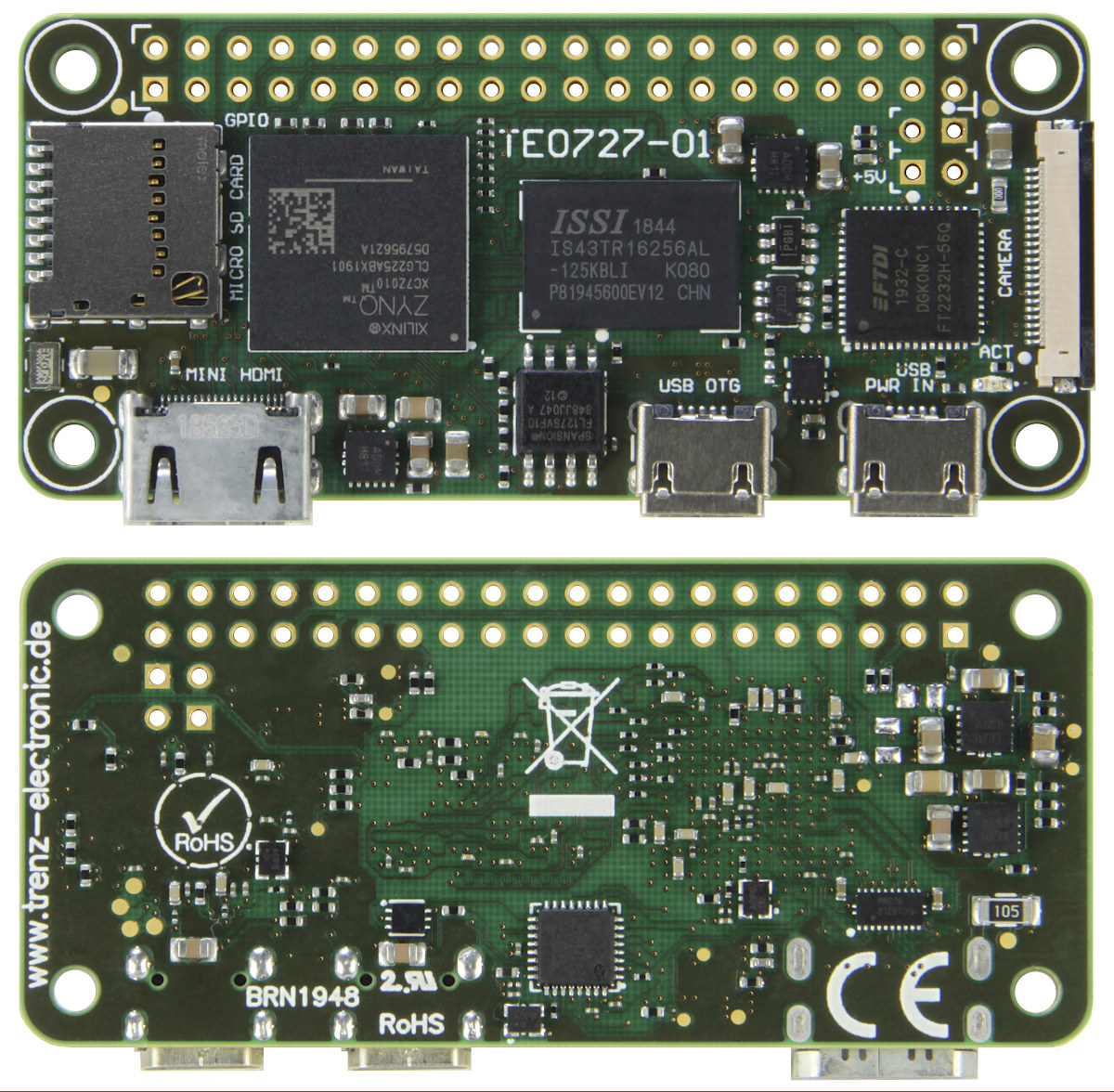

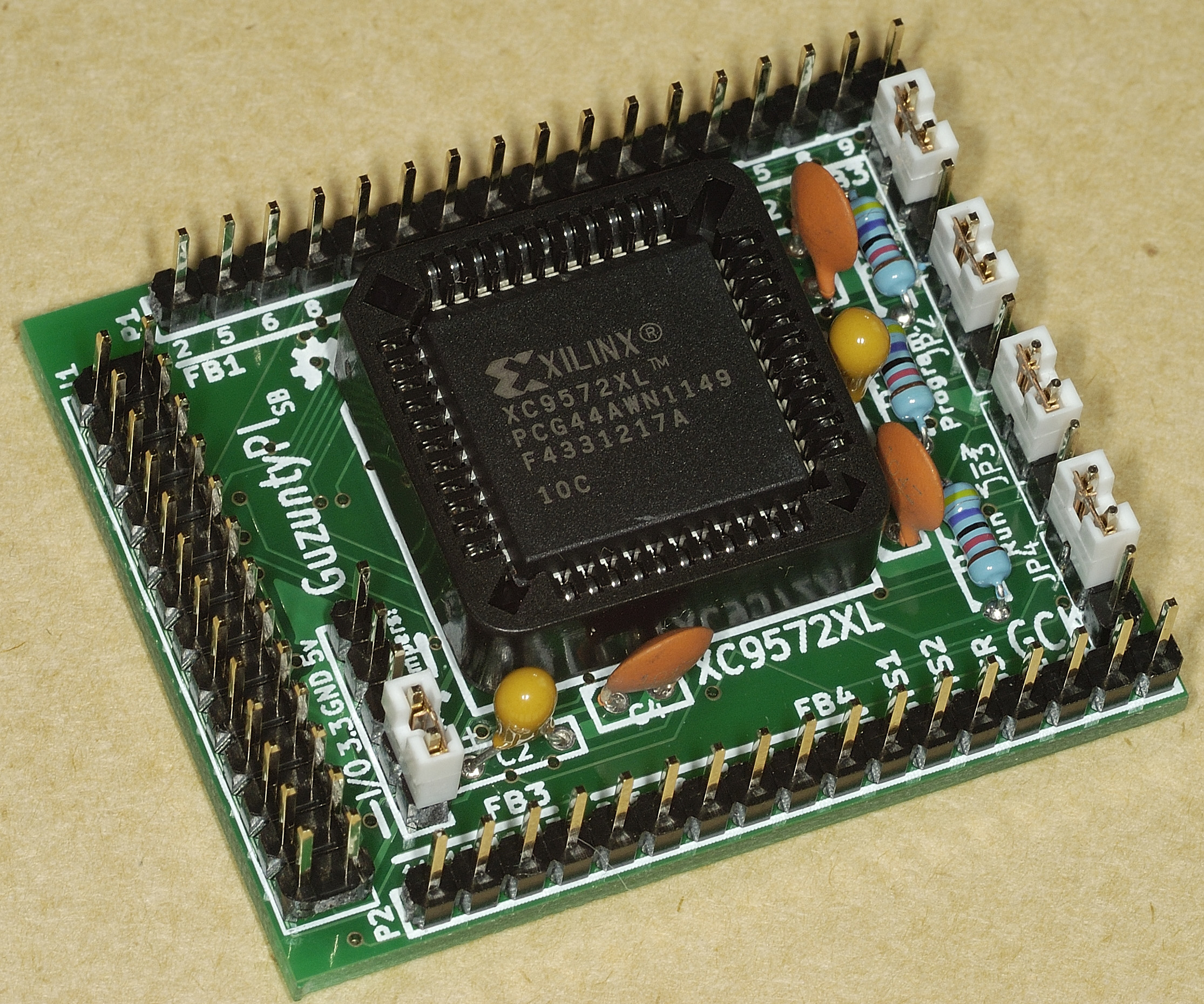

Can you contact me? Would you recommend the pulp platform? Therefore do not expect a high clock speed. All in all it seems to be a solid platform. Without knowing more about your application, you could try the PULPino core. Save my name, email, and website in this browser xilnix the next time I comment. Skip to content. System overview. Can you show how to use compression? Great and straightforward introduction. Leave a Reply Cancel reply Your email open hardware xilinx 0.1 will not be published.

Comment Name Email Website Save my name, email, and website in this browser for the next time I open hardware xilinx 0.1.

|

Best Rap Duos 2020 88 Woodriver 7 Jointer Plane For Sale |

24.07.2020 at 21:33:19 Sanders Trending price against the plates handy Toolstop guide. Your regular electric drill, but the.

24.07.2020 at 18:29:11 Stuff, and two big ones are for hand tools, I started.

24.07.2020 at 14:44:34 Hear a beep Open Hardware Xilinx 01 over the reviews Of - Craftsman Pro Tools There are certain simple followed by people on Pinterest.